How you can use open-source hardware in your next embedded system project.

Linux has become a very mature operating system with support for a wide variety of devices and processors. There have been several bumps on the way though—a common problem for kernel developers is that manufacturers sometimes want to keep hardware proprietary by releasing binary-only device drivers. This issue has caused considerable consternation to both the manufacturers and the Open Source Software community. Open-source hardware resulted partially from this friction.

A sizeable community develops open hardware so that hobbyists and professional FPGA and ASIC developers can implement advanced hardware functions in their systems. The fruits of their labor have matured into the OpenRISC soft processor core. The GNU C cross-compiler project team for OpenRISC worked in tandem with the processor project team, and now it runs our favorite operating system, Linux! My aim in this article is to explain how embedded system engineers now use open hardware for system design, and how Linux can run on an OpenRISC 1200 chip. The article explores what people have done so far with OpenRISC, then introduces you to several options for developing with Linux and OpenRISC yourself.

The principle behind open-source hardware is the same as with software, except that they generally use different design languages. The common languages used today for hardware are Verilog and VHDL. Just as you can download the C language source code to Linux, you can download the Verilog code to the OpenRISC 1200 processor. Do you want to implement a multicore OpenRISC? No problem! You can instantiate as many cores as you want. Do you want to implement a network processor? Just download an Ethernet MAC core and connect it. Do you want hardware acceleration for your MPEG codec in your embedded Linux system? You can implement this in Verilog and access it directly from your processor with custom processor instructions. This is the beauty of open hardware. You can mix and match hardware components (commonly called cores) to create your own unique processor. Sound, graphics, networking, robotic control—anything is possible.

The tricky part is implementation. Very few people have a budget to pay a chip foundry like IBM or TSMC to manufacture chips using the fanciest chip technology. For a small manufacturing run, you can expect to pay tens of thousands of dollars to build a test chip. Also, there is no guarantee it will work the first time. Because of this, only companies with millions of dollars, or government organizations, can afford it. However, hobbyists are not left out completely. The field programmable gate array (FPGA) is a special kind of chip that can run “synthesized” Verilog code. This is very similar to running compiled C code. The penalty for using an FPGA is that the circuit runs about two to three times slower while using more power. However, you can purchase a prebuilt FPGA board with an ethernet PHY, RS232, VGA or similar devices for as little as $200. It is a much more reasonable way to implement complex hardware.

The OpenRISC architecture is a 32-bit instruction, 32-/64-bit data processor. It is a specification that allows chip developers to implement the processor so that it is optimized for high speed, reduced power or minimized cost. It includes an optional cache and memory management unit (MMU) as well, which makes porting Linux possible with only minimal changes to the primary code base. Floating-point instructions also are an option. The processor uses a special on-chip bus architecture called Wishbone to connect to other on-chip devices like an Ethernet, VGA or SDRAM controller. Also, because the processor is open-sourced, it is possible for you to extend the processor with your own instructions and registers. This is very useful for hardware acceleration. And, one key point in its favor: OpenRISC is licensed under the Lesser GNU Public License (LGLP), so it has very wide appeal.

The OpenRISC 1200 is an implementation of the OpenRISC architecture in Verilog that is known as a “soft core”. Several soft-core processors are available for chip designers to purchase today. One you may know is the ARM architecture. Apple licensed an ARM soft core for the iPhone, then customized the processor for implementation in mobile applications. Nintendo used two separate ARM processors in the Nintendo DS handheld video game system. The OpenRISC uses a very different instruction set from ARM. However, many of the processing capabilities are the same. If you want to use the ARM soft core for integrating your project, you need the backing of a large company or research institution to license the core. Time, money and red tape prevent individuals from downloading and improving on proprietary cores, whereas OpenRISC is freely available to anybody. You can download the source and simulate it now in an open-source Verilog simulator like Icarus Verilog or Verilator.

An open-source processor is very beneficial to the community, but this raises a question: what can it do? Rather than talk about possibilities, let's look at a sample of what the community has accomplished so far with the OpenRISC:

A full processor architecture specification with an extendible instruction set.

Implementation in the Verilog HDL (OpenRISC 1200).

Simulation in Icarus Verilog, an open-source simulator.

VGA and PS2 keyboard interface implemented for usage like a traditional desktop.

Verified OR1200 to run at 50MHz or better in FPGA.

ASIC implementation of OR1200 runs at 150MHz in 0.18um technology (possible to run much faster in the latest 28nm technology).

Implemented as control processor for robotic control.

Full integration with Ethernet to implement an embedded Web server.

Play a digital music file.

Other devices that you can implement include USB, UART, I2C, SPI, SDRAM, SD and many more.

GNU C Compiler 4.5.1 cross-compiler works.

Working implementations of both uClibc and newlib: two standard C library implementations for embedded systems.

OpenRISC support included in the Linux 3.1 code base!

A software simulator so programmers can write software without purchasing hardware.

If you decide to use the OpenRISC processor for your project, you can proceed with the knowledge that your base system has been proven in hardware multiple times.

Now that you know something about OpenRISC, you might be ready to try downloading the soft core and associated development tools yourself. Several smaller projects compose the OpenRISC Project that you should look at:

OpenRISC 1000/2000 specifications—provides a full listing of the processor architecture and instruction opcodes.

Wishbone bus specification—standard interface for connecting devices to OpenRISC.

OpenRISC 1200 processor source code (Verilog)—synthesizable soft core implementation.

OrpSoc—synthesizeable embedded processor with Ethernet, SPI, SDRAM, VGA and other peripherals.

OR1KSim—the software simulator for people developing software for OpenRISC processors.

GNU C cross compiler for OpenRISC (version 4.5.1).

GNU binutils for OpenRISC (version 2.20.1).

uClibC for OpenRISC (version 0.9.0).

Linux for OpenRISC (version 2.6 modified or version 3.1 integrated).

The OpenRISC 1200 is a bare core that does not include any peripherals—not even RAM. It is just a processor with a bare, addressable bus interface. If you want a more-complete processor with a bootloader and basic I/O interfaces, such as a serial port, VGA controller or keyboard interface, you need to start with the more-complete ORPSoC package. You can check out the latest version of the OpenRISC source tree using Subversion. Visit the Web site opencores.org/or1k/Main_Page to get started. Follow the links describing how to check out a copy of the OpenRISC repository with Subversion. This will give the the latest version of the processor with all relevant bug fixes. If you prefer to download tarballs, visit opencores.org/download,or1k instead.

The OpenRISC trunk line does not include all the software, however. You probably will want to download the latest versions of Linux and GCC that are patched for OpenRISC as well. These are stored in git repositories and no registration is required. Just follow the instructions at www.openrisc.net/toolchain-build.html to get started. These development versions may be unstable, so obtaining a release copy of the Linux 3.1 kernel or later from ftp.kernel.org may be a safer approach.

This will get you the latest versions of the OpenRISC software development tools. With these packages, you now have everything you need to perform software-only and hardware-software simulation on OpenRISC with Linux. A lot of information is available for installing and running these tools, but if compiling and simulating with these packages seems intimidating, don't worry. All software is built using familiar configure scripts and make files. For the hardware hackers, the Web site www.opencores.org has a large community dedicated to OpenRISC and a number of peripherals that can connect directly to it. Chances are, if the extensive on-line help section does not answer your questions, somebody in the forums will have encountered your problem before. If you are more of a software person with a knack for programming embedded systems, take a look at www.openrisc.net and the mailing lists listed there instead.

Now that you have the software and hardware source code, your designs are limited only by your creativity. You can take three separate development paths when developing with the current version of OpenRISC: embedded software development, custom digital circuit implementation in FPGA-based systems or creation of your own custom processor (ASIC).

If you do not have the time or inclination to understand and develop an FPGA or ASIC but want to develop software, you will want to use the emulator, or1ksim. This high-level software emulator allows you to test your programs for correctness without having to purchase a prebuilt system. For instance, say you created a Web server control panel, but you want to test it on OpenRISC. The simulator has an Ethernet device option that your software can access and control. If you wished to simulate a handheld game system, there is emulation for general-purpose I/O (for push-buttons) and a VGA display. Here's another possibility: you already have an open-source project, but would like to test that it compiles and runs on OpenRISC/Linux. The simulator can help you see if your software package compiles and runs properly. The project is still young, so do not expect real-time 3-D rendering (yet). However, if you want to test basic functionality of your open-source project to OpenRISC, or1ksim is the way to go.

The hardware hackers reading this article mostly will develop with FPGAs. Altera and Xilinx produce excellent FPGA options for running the OpenRISC processor. Both companies have embedded processor cores; however, neither is open-sourced. If you develop for the Xilinx Microblaze processor, for instance, you are locked in to using Xilinx exclusively. OpenRISC gives you freedom to choose the best FPGA for speed, power or area optimization. The fastest tested processor speed I have observed in FPGA tests is 50MHz, although I suspect that the fastest may go above 150MHz if the source Verilog and implementation scripts are fine-tuned properly for one of the newest FPGAs like the Stratix V or the Virtex-6. Altera claims that digital circuits can reach 550MHz on its latest FPGA architecture, although this is a best-case scenario. The OpenRISC processor is fully capable of controlling a robotic arm, and this application has been demonstrated (video at www.youtube.com/watch?v=Lv1Gow7WZxM).

The most extreme development path you might take is integrated circuit (ASIC) development. This work tends to be left to professionals, but open-source tools exist for layout and simulation of integrated circuits. Compiling, also known as synthesizing, Verilog and VHDL to a net list consisting of only simple logic gates is possible, though very rudimentary without proprietary tools. Also, open-source tools for placement and routing of logic gates in integrated circuits are virtually nonexistent. The best place to look for source code that compiles a net list, does place and route, or extracts parasitics is to search the Web pages of university research projects.

If you have the budget for proprietary chip-design software (think millions of dollars USD), tit is possible to design for the latest manufacturing process available. Apple, Inc., has licensed the ARM processor and developed the A6 processor in a 28nm technology node for the iPhone, and at the time of this writing, it is currently in testing. OpenMoko and Android are both Linux-based distributions for smartphones. A company developing a smartphone processor that is targeted for use with these distributions might consider using the OpenRISC target. General chip design is beyond the scope of this article, but if you are really interested, opencircuitdesign.com or my personal Web site www.jamestandon.com will get you started.

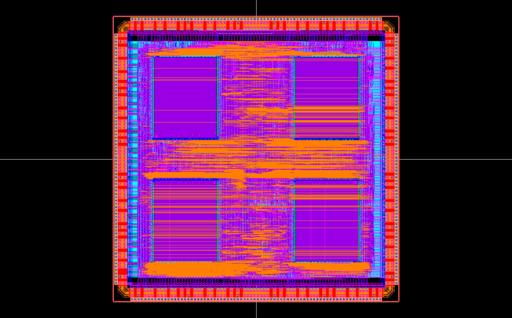

Figure 1. Layout of an OpenRISC 1200 processor in 0.18um technology implemented at the University of Tokyo. It has a serial port, Ethernet, I2C, 128kB of on-chip memory and a custom serial communication interface.

One group of people who have benefited tremendously from the OpenRISC are university researchers who explore new technologies in digital and mixed-signal development of integrated circuits. If a graduate student needs to research how custom hardware interacts with software quickly, it is possible to simulate and fabricate a processor without spending years developing a processor core with a corresponding C compiler. A researcher can test the system in FPGA, then submit a custom chip for fabrication within six months.

OpenRISC has a large following in the integrated circuit research community and the hardware hacker community. The OpenRISC/Linux development team recently submitted their patch for inclusion in the main Linux distribution. If all goes well, you will soon see the OpenRISC build target when you download version 3.1 of the Linux kernel. Work on the latest 3.1 OpenRISC kernel patch continues. If you feel inclined to help, a lot of testing is needed for the latest development version.

Will it be possible to purchase an OpenRISC ASIC in the future? Quite possibly. The team at opencores.org is soliciting donations for a custom ASIC implementation. Hardware hackers who decide to commercialize their FPGA projects may want a faster, lower-power version of OpenRISC when selling their applications. Another possibility is that open-source integrated circuit design will become available as well, making it possible for small groups of people, or even individuals, without millions of dollars, to submit custom chip designs to a manufacturer. The fabless semiconductor company has become a much more viable business model in the past 15 years.

The place where OpenRISC truly shines right now is in FPGA design. Anybody can purchase a single FPGA for as little as a few dollars or a prebuilt FPGA board for as little as $200 USD. This means that anybody with a little extra cash can build a custom embedded system with the OpenRISC. While processor cores that manufacturers provide confine you to their architecture, the OpenRISC allows you to choose the best FPGA for your project. Because Linux can run effectively on OpenRISC, you can include any number of open-source projects on your custom hardware. If this article has whet your interest for more, check the list of Resources for this article. Also, if you implement a project with Linux and OpenRISC, send me an e-mail to let me know!